------樊渝江

這是我寫的第1次Cadence筆記,寫的不是很好希望大家糾正。

之前1直使用的是Cadence 15.7,這次由于要使用埋阻埋容工藝所有更改成了16.5,16.5給我的感覺是很多工具都變位置了,還是摸索了1下才找到的,但封裝和原理圖的制作界面沒怎樣變還是保存之前界面。

開始我們的埋阻埋容設計了。

1.原理圖網表輸出。

為了方便我就不細說原理圖是怎樣建立的了,和15.71樣的沒甚么區分。

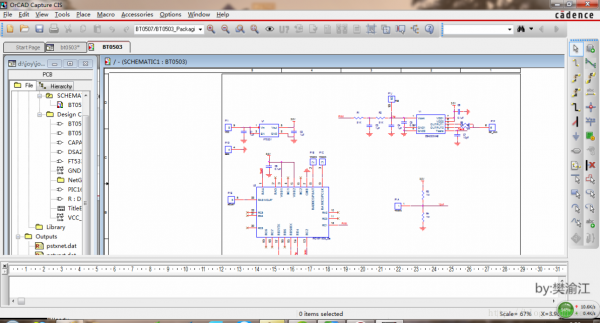

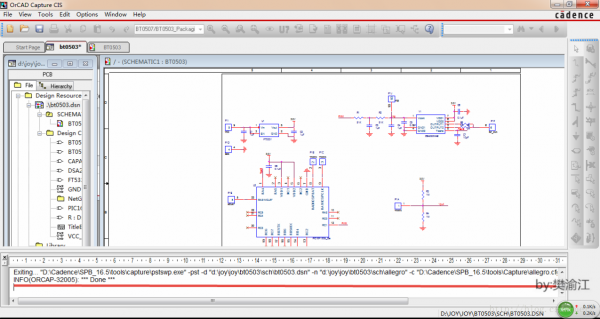

上圖就是我建好的原理圖,在導出網表之前我們要把每一個期間的封裝添上,然落后行DRC檢查要不然在導網表的時候會報錯。(我已把封裝添加進去了)

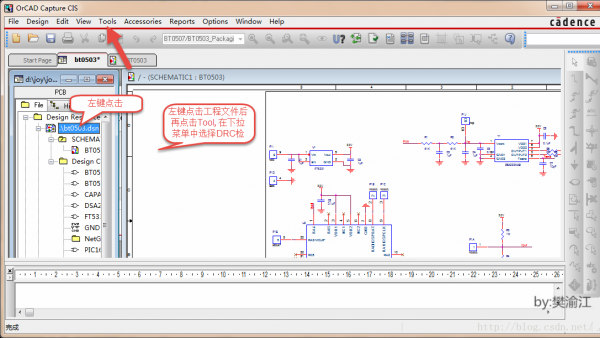

先運行DRC檢查,左鍵點擊工程文件,等菜單欄變化后,點擊Tools – Design Rules Check..

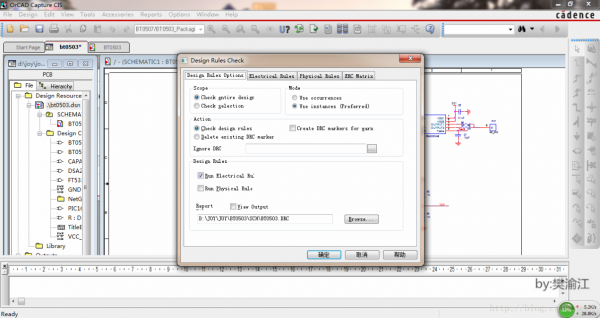

然后會彈出出以下對話框

這個對話框就是DRC校驗的設置對話框,如果沒的特殊要的話,直接默許設置就OK了(15.7需要自己選,16.5默許的已完全足夠了)。

軟件就開始直接檢查,有毛病就會彈1個對話框出來告知你問題在哪,沒有錯就會直接通過。

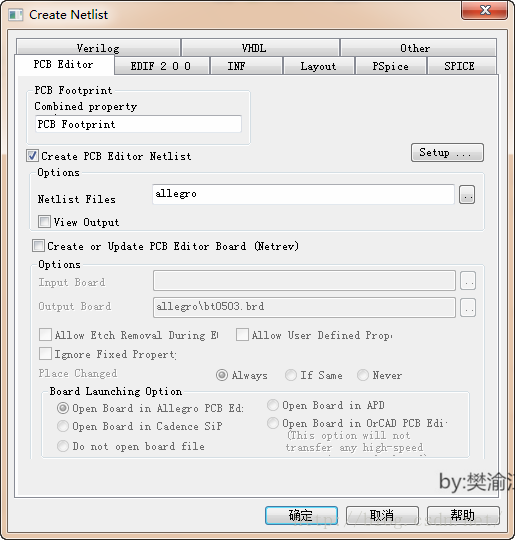

DRC檢查過后下1步就開始導出網表,點擊Tools –Create Netlist,就會出現以下對話框。

第1次導出網表就把Create PCB Editor Netlist 那欄打上勾,網表輸出的路徑就是在你原理圖工程下,成功后會多1個allegro的文件夾,里面就有網表。

開始導出網表。

出現紅色劃線部份說明導出成功了,否則會彈出1個對話框告知你有毛病的地方。

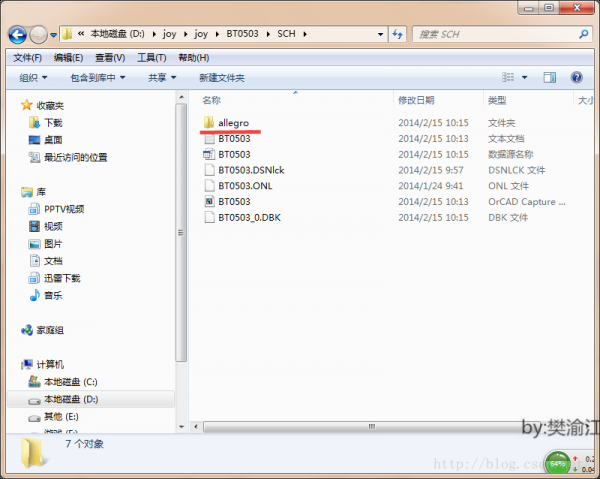

網表導出后多的1個文件夾。

2.建立PCB工程

建立PCB工程文件我相信譽過cadence的都會,操作沒有變。

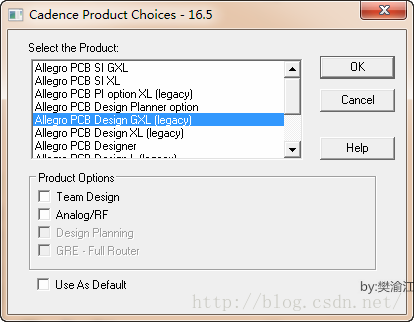

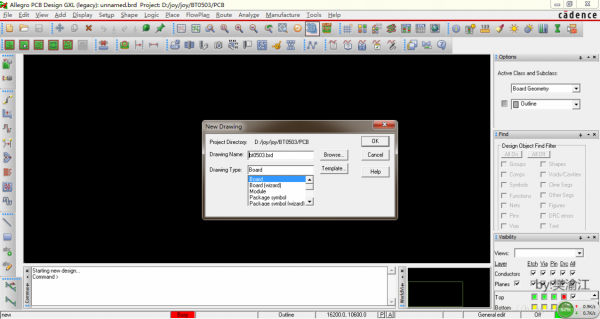

點開 PCB Editor 出現下面對話框,選擇版本就OK了,GXL就是功能最多的。

進入界面后點擊File – New 就會出現下面對話框,選擇board,添上工程名,選擇存儲路徑,點擊OK。就建好PCB工程了(扼要帶過,會cadence的應當都非常清楚)。

3.界面參數設置

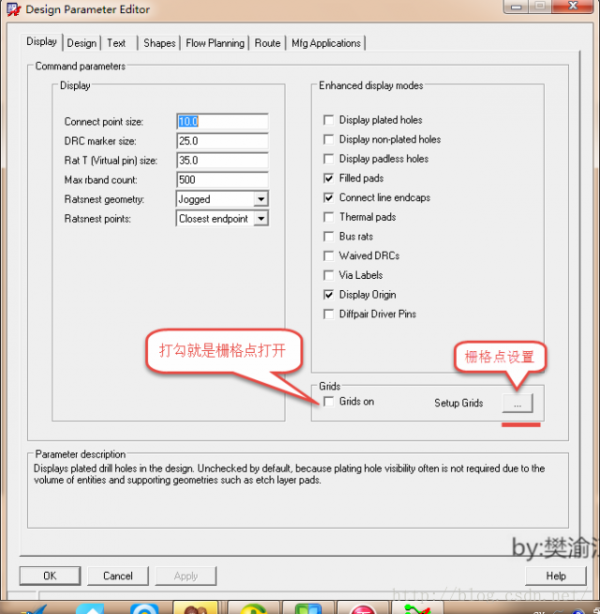

我們需要設置頁面大小,還有柵格點,這樣方便我們后續的工作

先是柵格,點擊setup – Design Parameter Editor,出現下圖

點擊柵格點設置就會出現下圖

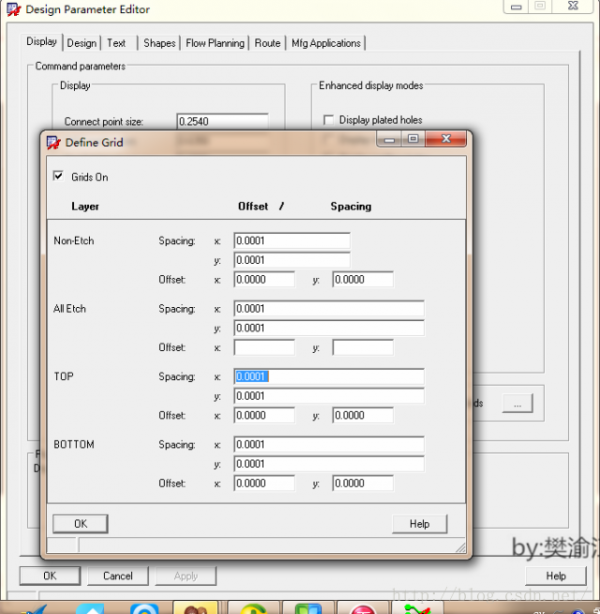

里面有頂層、底層、電氣層的柵格點最小間距設置,x和y分別代表x軸方向和y軸方向的柵格點,由于我的板子很小所以我設置的是最小。

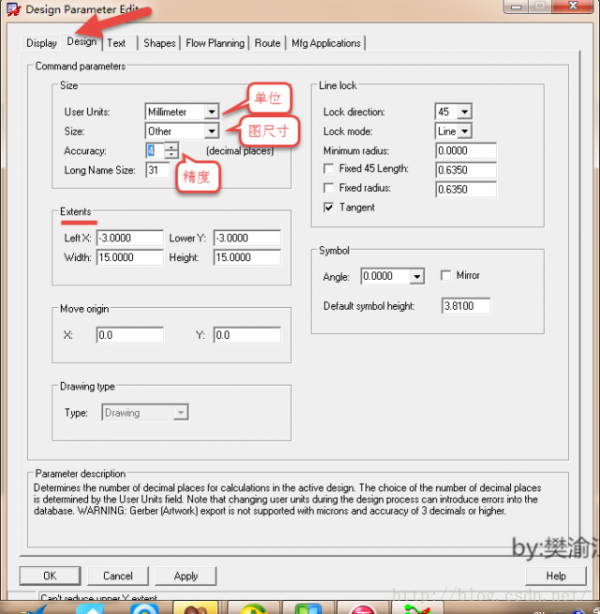

下1步是設置頁面和全部工程使用的距離單位、距離精度。

Extents 里面是設置圖紙大小(圖紙尺寸欄選擇了 other ,這就能夠設置)和設置原點位置(網上有許多教程講這個)。精度欄最大的就是4了。單位我們選擇毫米。

4.導入網表

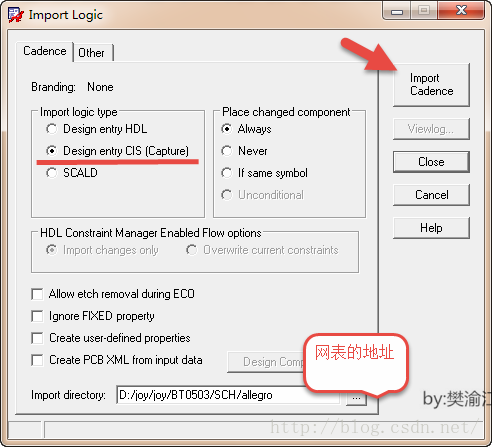

點擊File – Import – Logic 就出現下圖

第1次導入網表的時候要選擇網表的路徑,就是剛才導出原理圖網表的路徑,然后選擇生成網表的工具,我們是用的Cadence自帶的原理圖工具(就是有劃紅線的選項),如果是其他軟件做的網表就要選other。最后點擊Import Cadence 網表就成功導入了。

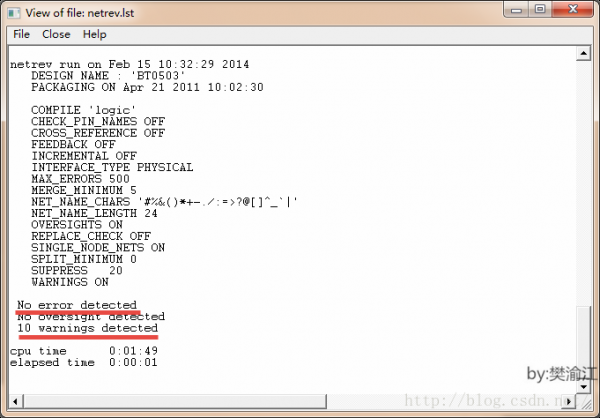

以上就是導入網表后的反饋信息,可以看見毛病和正告。

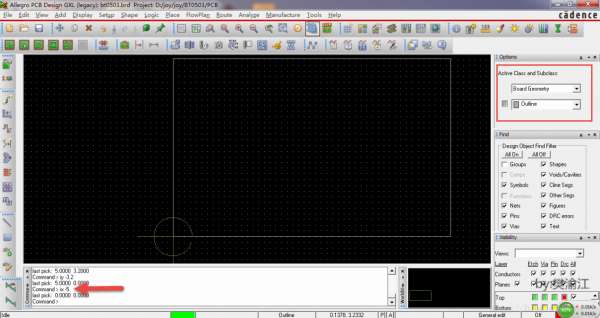

5.PCB板外框設計。

PCB外框需要畫出物理外框、布線區域、器件放置區域,這幾個是最重要的,有其他需要就添加其他的。

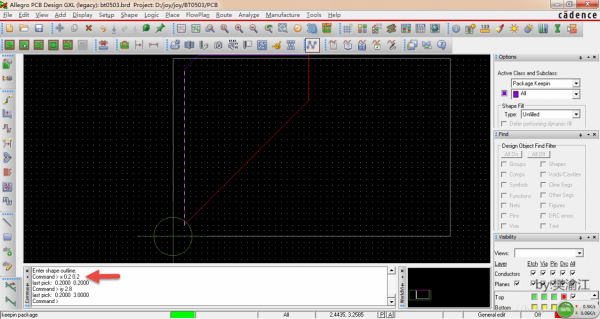

首先添加外框點擊Add – Line 選擇所屬類(右側紅框內)。Line是走線的意思,可以手工畫1個框也能夠坐標畫。我的圖是用坐標畫的,點擊Line和選好類后在指令欄中輸入 x 0 0(從原點起畫,x和0、0和0之間有個空格)點回車,iy 3.2(向Y軸正向畫3.2mm) 點回車,ix 5(向x軸正向畫5mm)點回車, iy ⑶.2(向Y負向軸畫3.2mm)點回車,ix ⑸(向x軸負向畫5mm)點回車,1個方框就行了,也能夠直接輸4個頂點的坐標畫全部方框。

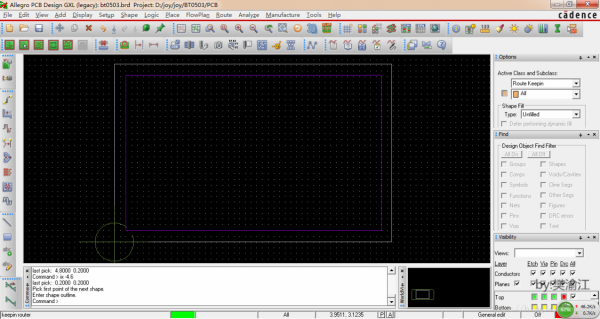

外框畫好后就是開始畫允許布線區域和允許期間放置區域

點擊 setup – Areas – Package Keepin 和 Route Keepin畫方框,方框的大小依照廠家的標準最好(1般都比外框小0.2mm)。

6.板層設置

點擊Setup – Cross Setion

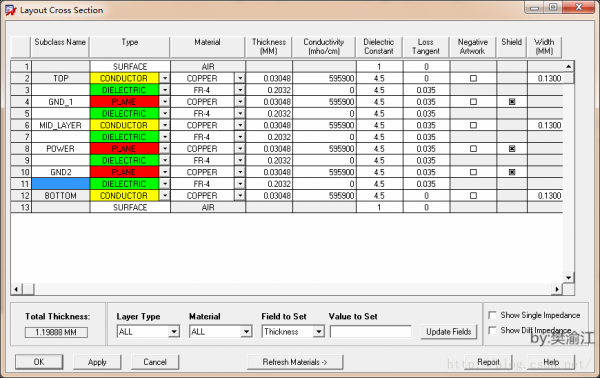

默許的時候只有頂層和底層,我們需要添加層,具體按自己的需求吧,我們這是6層。

就需要設置1下,在前面的序號上點擊鼠標右鍵,會出現1個下拉框里面有兩個選項 Add Layer Above(在當前層之上添加) 和 Add Layer Below(在當前層之下添加)。然后添加4層,每層之間需要1個介質層,默許選擇就能夠。現在設置每層的屬性,在Type這1欄選擇,中間的地層和電源層選擇平面(plane),需要埋阻埋容層必須設成導電層。

下圖就是我針對我的PCB設置的板層結構。

層設置好了就需要對埋阻埋容進行設置

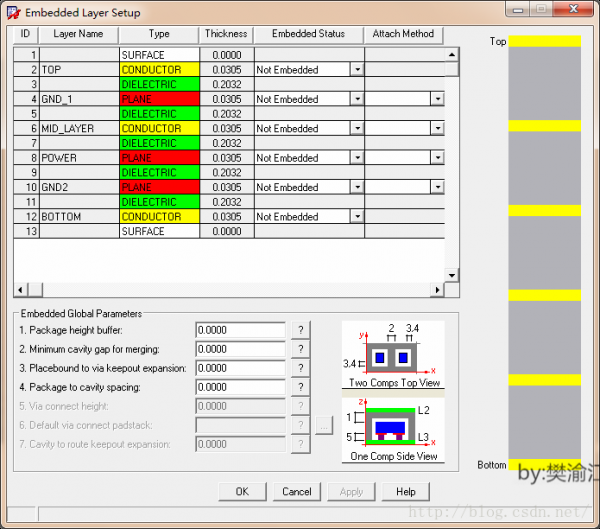

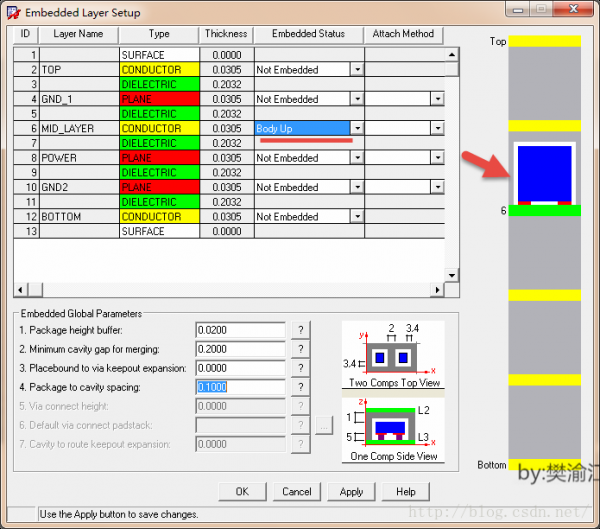

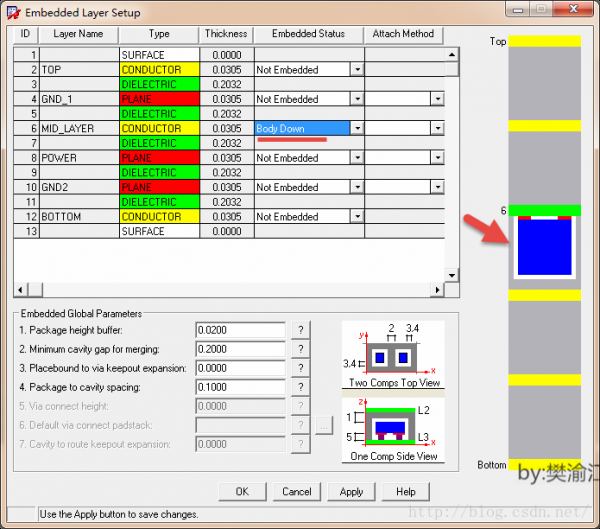

點擊Setup – Embedded layer Setup出現下面對話框

我們需要設置我們的第3層埋阻埋容,以下圖

其中上半部份為疊層設置,Embedded Status設置埋入式器件狀態,即設置內層器件方向:Body up表示器件在內導電層之上;Body down表示器件在內導電層之下;Not Embedded表示該疊層不允許放置埋入器件;Protruding Allowed表示允許器件突出,即允許該內層下方或上方的導電層凸出本層,以下圖所示。Attach Method用以設置埋入式器件的連接方式,包括:Direct Attach表示埋入式器件直接連接內電層;Indirectly Attach表示埋入式器件非直接連接上內電層,即以焊盤連接到內電層向外連接。

下半部份Embedded Global Parameters全局埋入式器件的疊層設置參數,其意義在右側的坐標中有對應顯示,包括: Package height buffer:定義埋入式器件腔體與相鄰疊層的距離限制; Minimum cavity gap for merging:定義腔體合成的最小距離,如25mil,即兩個埋入式器件腔體間距接近至25mil以下時,兩腔體即作甚1個腔體; Placebound to via keepout expansion:定義器件的封裝Placebound到器件外部制止放置過孔區域的延伸距離; Package to cavity spacing:定義器件封裝外部至埋入式腔體的間距; Via connect height:定義埋入式器件向外連接時,所用過孔的高度; Default via connect padstack:定義默許情況,允許和埋入式器件向外過孔相連接的焊盤類型; Cavity to route keepout expansion:定義埋入式器件腔體至該疊層制止布線區域之間的間距。

7.器件設置

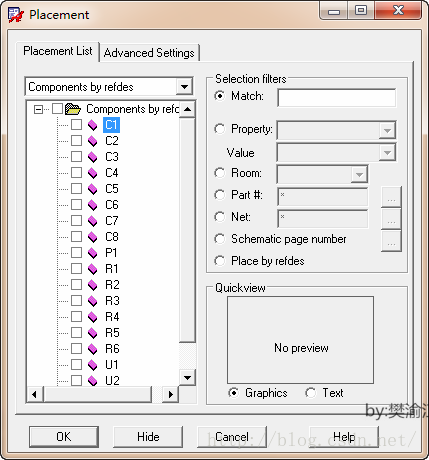

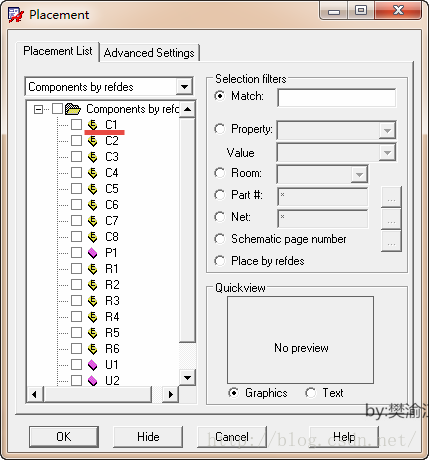

左側是沒有設置電阻電容可以埋入,右側是設置了電阻電容可以埋入。

具體設置以下:

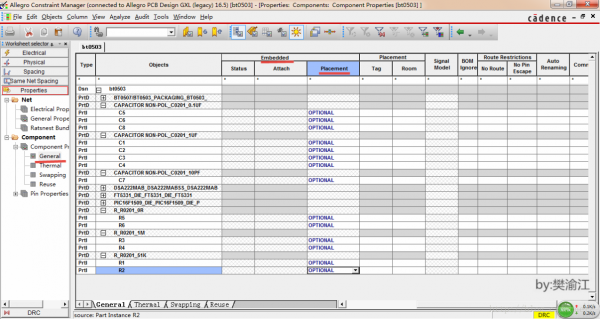

點擊Setup – Constraints – Constraint Manager ,會出現以下對話框

在Embedded屬性欄中,Placement列用以定義器件的埋入式屬性,為某個器件定義Embedded/Placement屬性,這些器件就能夠在PCB中作為埋入式器件放入PCB內層,該屬性包括:Option可選埋入式,則該器件可放在表面層,也能夠作為埋入式器件放入內層;Required必要埋入式屬性,則該器件必須作為埋入式器件放在內層,不可以置于表面層;External Only只外置屬性,則該器件只能放在表面層,不可以作為埋入式器件置于內層。

8.放置器件

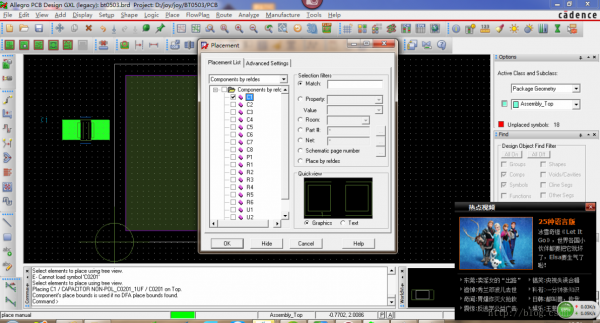

點擊place – Manually 出現以下對話框,在器件前打勾就能夠放置器件了(不要點OK)直接移動鼠標就能夠看到器件隨著鼠標走,點擊鼠標右鍵有1個選項Place On Layer 里面有各個層的名字,點擊就能夠將器件放置到對應的層去,默許的是頂層。

如果放置器件的時候出現毛病,沒有器件隨著鼠標移動,那說明是你的庫沒有導進來。

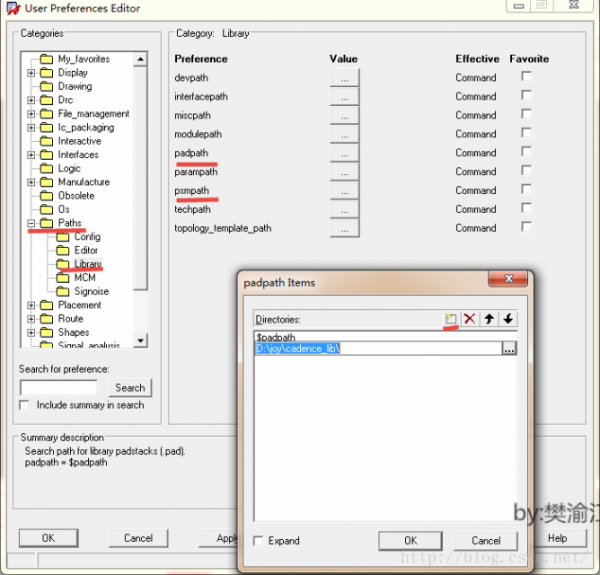

點擊 Setup – User Preferences 出現下圖

把紅線部份東西點擊,導入你的pad和封裝的庫,就OK了。

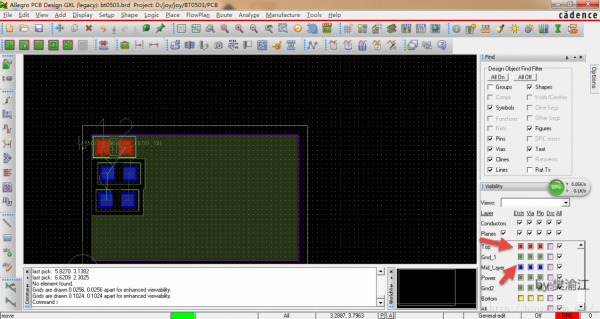

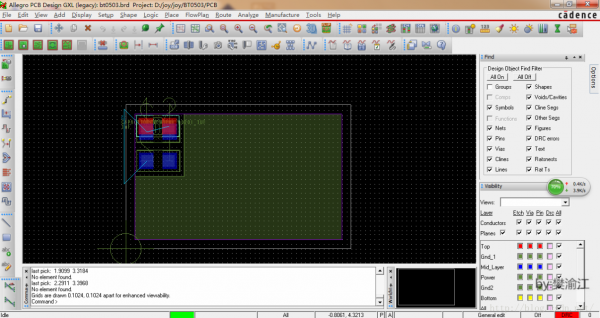

以下是放置好后的器件

紅色是頂層,藍色是中間層了。

大功告成,頂層和中間層都放有器件。

如果兩個期間像上圖那樣有堆疊的時候,需要修改1下DRC,由于他默許2維空間里這兩個器件堆疊了,但是在3維空間里他們是沒有堆疊的。

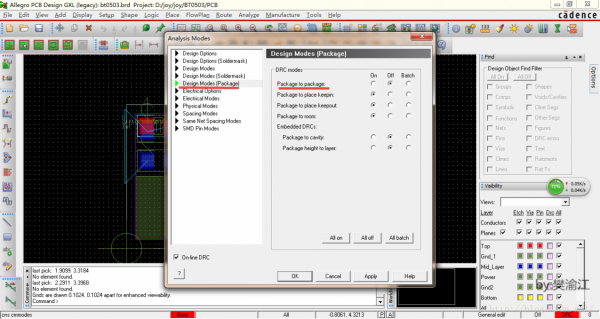

點擊Setup – Constraints –Modes 出現下圖

把紅線部份選成off就行了。

全部埋阻埋容的設計就OK了,剩下的就是布局布線了。這個我相信大家都能弄清楚的。